How Do Hardware Interrupts Work: A Practical Guide

Explore how hardware interrupts work, from signal generation to ISR handling, latency, and prioritization. A practical, hands-on guide by The Hardware for builders, DIYers, and technicians.

Hardware interrupts are asynchronous signals that momentarily pause the main program to service a peripheral event. They are triggered by devices like timers, serial interfaces, or external pins and cause control to jump to an interrupt service routine (ISR). According to The Hardware, interrupts enable efficient, responsive systems by letting the CPU focus on time-critical tasks only when needed. They require careful design to avoid missed events or excessive latency.

What are hardware interrupts? A concise definition and motivation

Hardware interrupts are asynchronous signals that momentarily pause the main program to service a peripheral event. They are triggered by devices like timers, serial interfaces, or external pins and cause control to jump to an interrupt service routine (ISR). According to The Hardware, interrupts enable efficient, responsive systems by letting the CPU focus on time-critical tasks only when needed. They require careful design to avoid missed events or excessive latency.

// Minimal interrupt example (pseudo-C)

volatile int irqFlag = 0;

void MyDevice_IRQHandler(void) {

irqFlag = 1;

// Clear the interrupt flag in device-specific register

}; Simple interrupt stub (pseudo-assembly)

ISR_EXIT:

pop r0

reti- Note the difference between edge-triggered and level-triggered interrupts.

- Edge triggers fire once on a transition; level triggers remain asserted while the line is high.

Hardware interrupt routing and the interrupt controller

Every interrupt originates from a peripheral line and travels through an interrupt controller before reaching the CPU. On ARM Cortex-M systems, the Nested Vectored Interrupt Controller (NVIC) manages priorities, enables, and vectoring. The interaction between the peripheral, the NVIC, and the CPU defines latency, masking, and nesting behavior. The Hardware analysis, 2026 highlights that clean priority schemes reduce jitter and missed events.

// Enable timer interrupt in NVIC (CMSIS-style)

NVIC_EnableIRQ(TIM2_IRQn);// Sleep until the next interrupt (common power-saving pattern)

while (1) {

__WFI(); // wait for interrupt

// waking condition handled in ISR

}- Use a vector table to map IRQn numbers to ISRs.

- Prefer a single, well-documented ISR per peripheral.

Latency, priority, and nesting in interrupts

Interrupt latency is the time from an event triggering an interrupt line to the first instruction executed in the ISR. This is affected by clock speed, memory hierarchy, interrupt masking, and priority grouping. The Hardware Analysis, 2026 notes that explicit priority grouping helps mitigate priority inversion and ensures time-critical tasks run promptly. A good practice is to assign clear priority levels and document their impact in datasheets.

// Priority grouping and per-IRQ priority

NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4);

NVIC_SetPriority(TIM2_IRQn, 1); // high priority

NVIC_SetPriority(USART1_IRQn, 3); // lower priority// Nested interrupt example (pseudo)

void HIGH_priority_ISR(void) { /* fast, minimal work */ }

void LOW_priority_ISR(void) { /* only runs when no high-priority tasks */ }- High-priority ISRs should do minimal work and defer processing.

- Use flags or a queue to communicate with the main code.

Writing safe ISRs and sharing data with the main context

Are you allowed to call printf or malloc inside an ISR? Generally no. ISRs should be short, avoid blocking calls, and share data via volatile variables or lock-free structures. Protect shared state with minimal critical sections and memory barriers when needed. The Hardware's recommended pattern is to set a flag or enqueue a small item and process it in the main loop or a deferred handler.

volatile uint32_t eventCount = 0;

void TIM2_IRQHandler(void) {

if (TIM2->SR & TIM_SR_UIF) {

TIM2->SR &= ~TIM_SR_UIF; // clear flag

eventCount++; // signal main loop

}

}// Safe data exchange using a ring buffer (simplified)

volatile uint8_t rxBuffer[128];

volatile int rxHead = 0, rxTail = 0;

void USART_IRQHandler(void) {

uint8_t c = READ_USART_DATA();

rxBuffer[rxHead++] = c;

}- Prefer posting work to the main context rather than doing it in ISR.

- Always clear the interrupt source to avoid retriggering immediately.

Steps

Estimated time: 60-120 minutes

- 1

Define interrupt goals

Identify the peripherals that will generate interrupts and set clear goals for latency, jitter, and nesting. Document which events must be serviced promptly and which can be deferred.

Tip: Start simple: pick one IRQ source and validate end-to-end flow before adding more. - 2

Choose MCU and interrupt sources

Select a microcontroller with a suitable interrupt controller (NVIC, GIC, etc.). List the sources you will enable and how they map to ISRs.

Tip: Check datasheet for initial priority defaults and any hardware quirks. - 3

Enable clocks and peripheral interrupts

Turn on the timer or device clock, enable the specific IRQ, and verify vector table mapping to the right ISR.

Tip: Remember to clear any pending flags before enabling to avoid spurious triggers. - 4

Implement and register ISRs

Write tiny, fast ISRs that set flags or enqueue work, and keep the heavy processing in the main loop or a deferred handler.

Tip: Avoid blocking calls inside ISR; use volatile/shared state correctly. - 5

Test and measure latency

Use a controlled test to measure interrupt latency and validate that high-priority ISRs preempt lower-priority tasks as expected.

Tip: Use deterministic test benches and repeatable timing sources. - 6

Refine and optimize

Iterate by adjusting priorities, reducing ISR work, and optionally adding deferred processing for complex tasks.

Tip: Document changes and re-run latency tests after each adjustment.

Prerequisites

Required

- Required

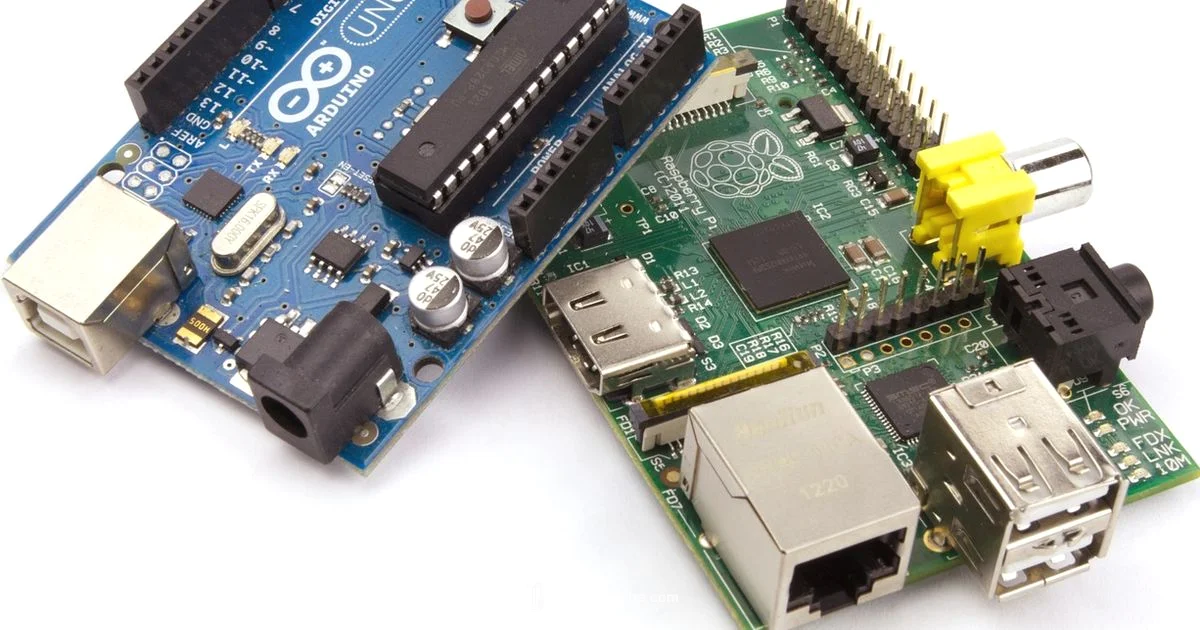

- ARM Cortex-M or AVR microcontroller development boardRequired

- Required

- Debugging hardware with a programmer/debugger (JTAG/SWD)Required

Optional

- Basic electronics and digital logic understandingOptional

- Reading datasheets for IRQs and registersOptional

Keyboard Shortcuts

| Action | Shortcut |

|---|---|

| Build/Compile projectIn most IDEs like VS Code or Eclipse | Ctrl+⇧+B |

| Flash/upload firmware to MCUUse vendor toolchain for the target MCU | Ctrl+Alt+U |

| Open serial monitorMonitor UART/USART output | Ctrl+⇧+M |

| Start/stop debuggingAttach debugger and run the firmware | F5 |

| Step over / Step intoNavigate through code while debugging | F10 / F11 |

| Reset targetReset the MCU during development | Ctrl+R |

FAQ

What is the difference between an IRQ and an ISR?

An IRQ (interrupt request) is the signal line or event that asks the CPU to pause current work. An ISR (interrupt service routine) is the tiny piece of code that runs in response to that IRQ. The ISR should be short and simply signal the main program or perform minimal work, deferring heavier tasks to the main loop or a deferred handler.

An IRQ is a signal; the ISR is the tiny handler that runs because of that signal. Keep ISRs short and pass bigger work back to the main program.

Why is interrupt priority important?

Priority determines which interrupts preempt others when multiple devices request CPU time. A well-defined priority scheme minimizes latency for critical tasks and reduces the chance of priority inversion, where a low-priority task blocks a high-priority one. The Hardware analysis emphasizes documenting and validating these priorities.

Priorities let the CPU decide which interrupt gets serviced first, which keeps critical tasks responsive.

Can ISRs call blocking functions or do long operations?

Generally no. Blocking operations can stall other interrupts and delay system response. ISRs should be fast, set a flag or enqueue work, and return quickly. If you need heavy processing, do it later in the main loop or a dedicated task.

No, ISRs should stay short and avoid blocking calls.

What is interrupt latency and how can I measure it?

Interrupt latency is the time from event trigger to first ISR instruction. Measure it with precise timing tools on your hardware, using known clocks and controlled triggers. The Hardware notes that architecture greatly influences latency, so tailor measurements to your target MCU.

Latency is how long a trigger takes to wake the ISR; measure it with a fixed clock and repeatable trigger.

How do I debug interrupts on real hardware?

Use a debugger or logic analyzer to observe ISR entry/exit and vector tables. Start with a single IRQ, confirm vector binding, then expand. Ensure the ISR clears its source and that shared data is handled safely.

Debug interrupts by watching the ISR appear and exit in the debugger, and confirm the right IRQ is firing.

Main Points

- Understand what a hardware interrupt is and when it triggers

- Write minimal, fast ISRs and defer work

- Configure a clear priority scheme to control latency

- Test interrupt latency in real hardware

- Document ISR behavior and data sharing rules